Modeling Remapping Based Fault Tolerance Techniques for Chip Multiprocessor Cache with Design Space Exploration | SpringerLink

Energy Efficient Dim and Dark Cache for Temperature Reduction of Chip Multiprocessors | Bentham Science

Microprocessor Architecture: From Simple Pipelines to Chip Multiprocessors: Baer, Jean-Loup: 9780521769921: Amazon.com: Books

Chip Multiprocessor Architecture: Techniques to Improve Throughput and Latency (Synthesis Lectures on Computer Architecture) (Paperback) | Hooked

Embedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case Studies / Edition 1 by Katalin Popovici, Frïdïric Rousseau, Ahmed A. Jerraya, Marilyn Wolf | 9781461425670 | Paperback | Barnes & Noble®

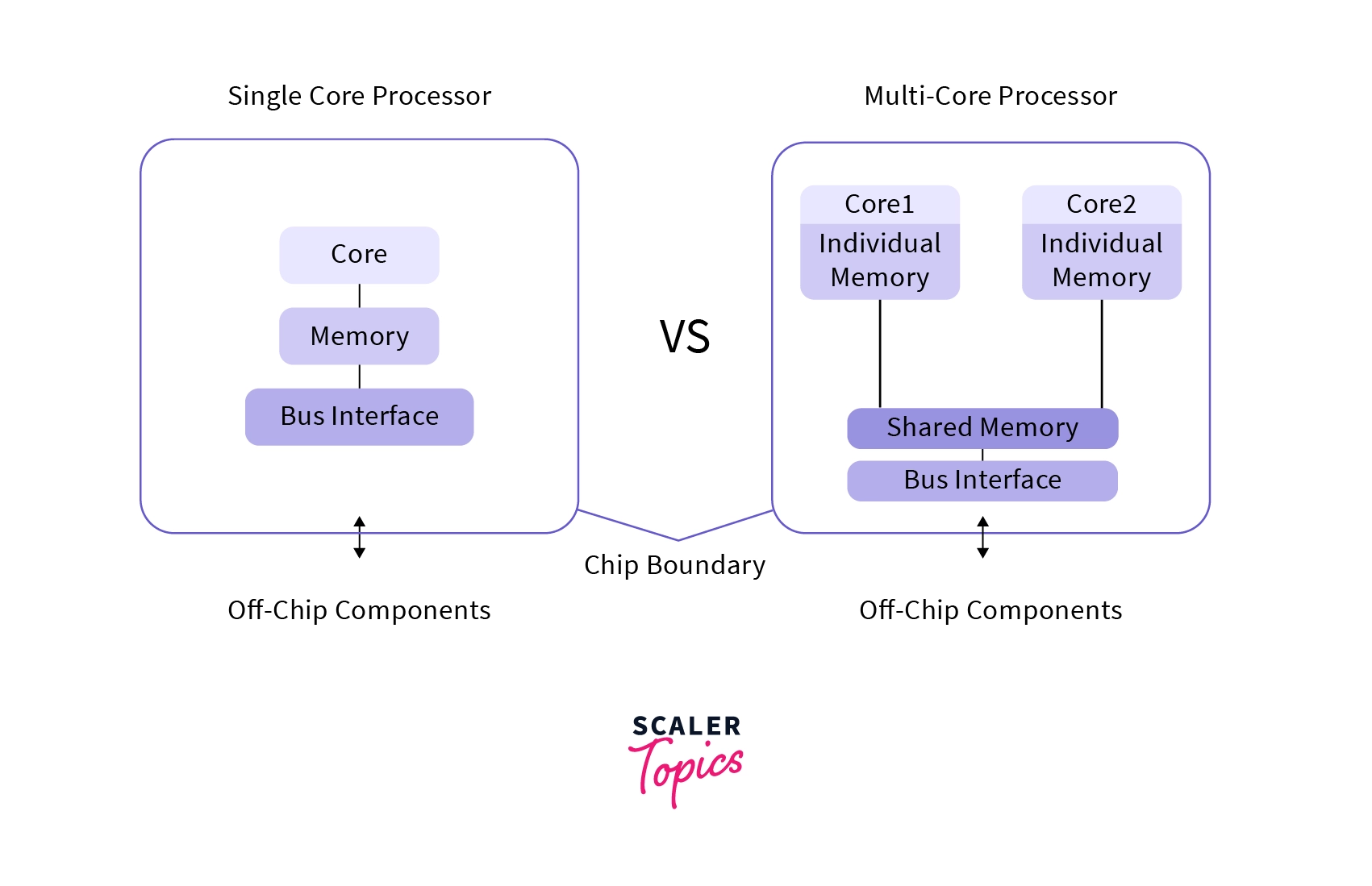

JLPEA | Free Full-Text | Architectural Techniques for Improving the Power Consumption of NoC-Based CMPs: A Case Study of Cache and Network Layer

Amazon.com: Embedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case Studies (Embedded Systems) eBook : Popovici, Katalin, Rousseau, Frédéric, Jerraya, Ahmed A., Wolf, Marilyn: Books

A Multiprocessor System-on-chip Architecture with Enhanced Compiler Support and Efficient Interconnect

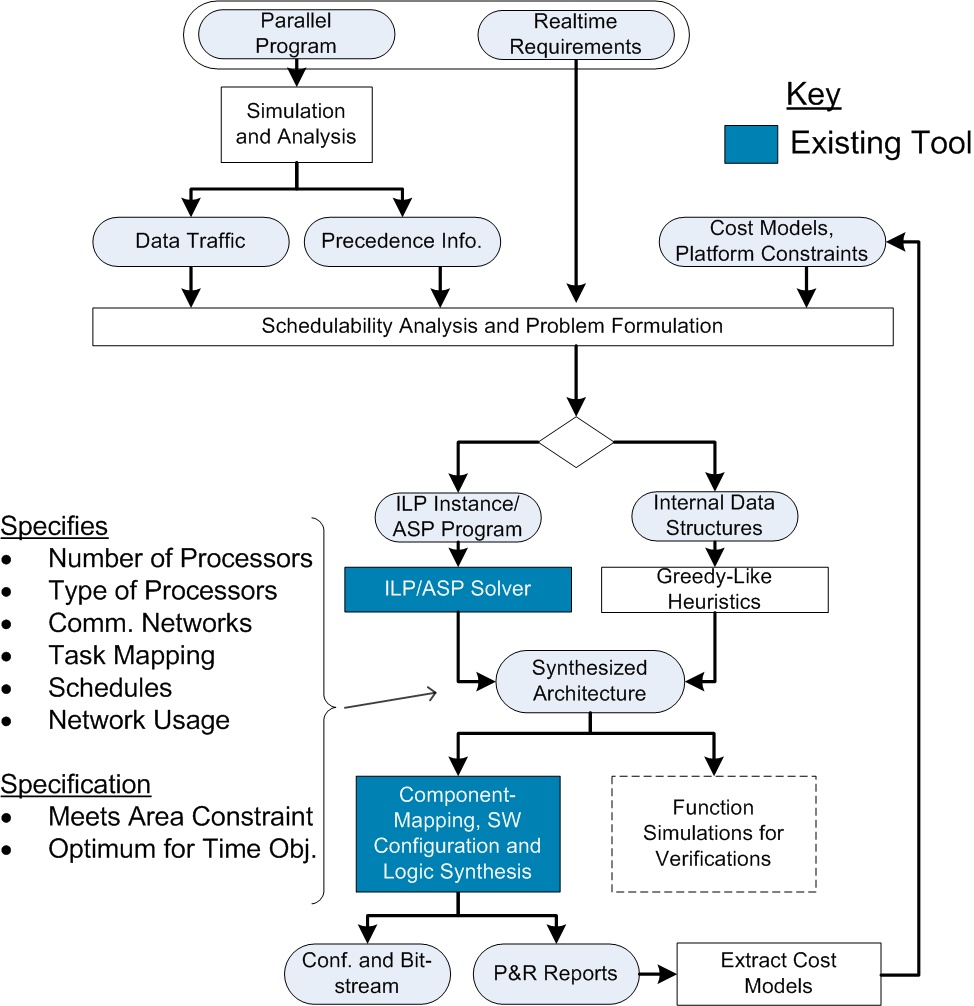

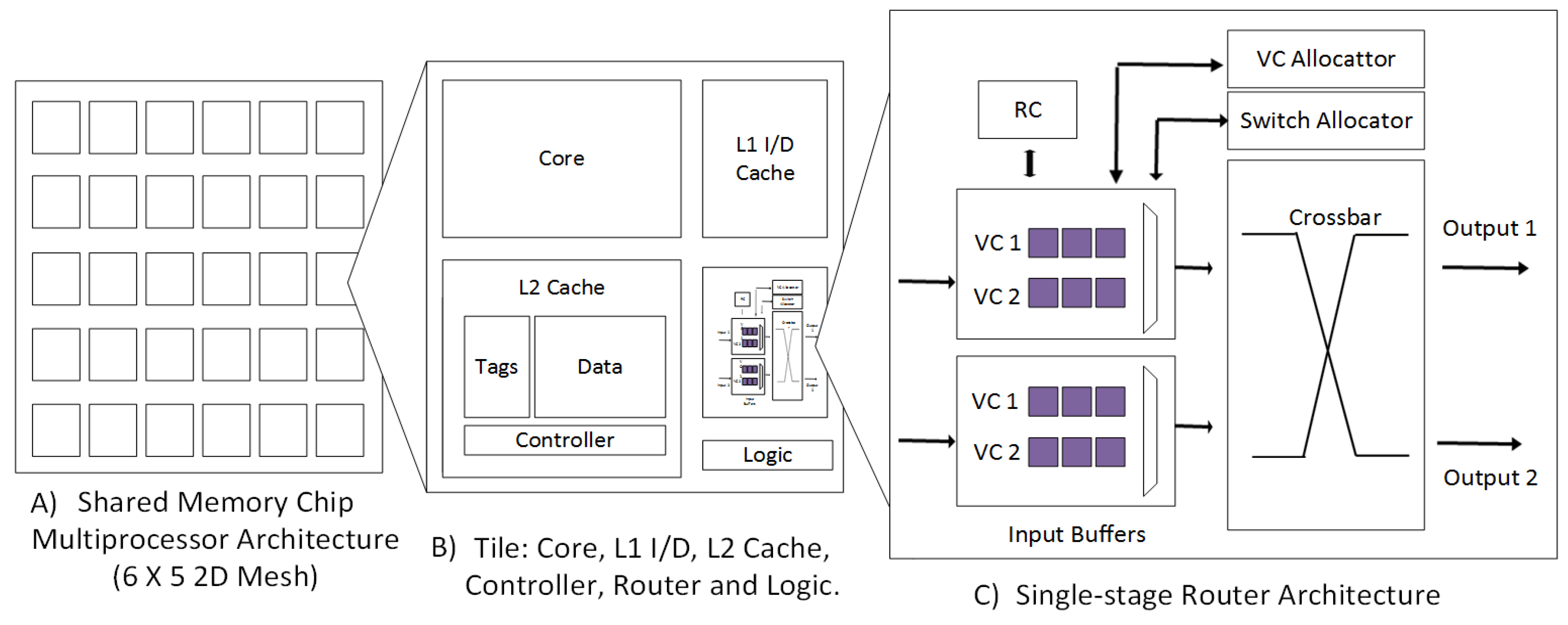

![PDF] An adaptive chip-multiprocessor architecture for future mobile terminals | Semantic Scholar PDF] An adaptive chip-multiprocessor architecture for future mobile terminals | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/2058c3bf1debcccbfaf5a6c29f7a18d7a820ca5c/2-Figure1-1.png)

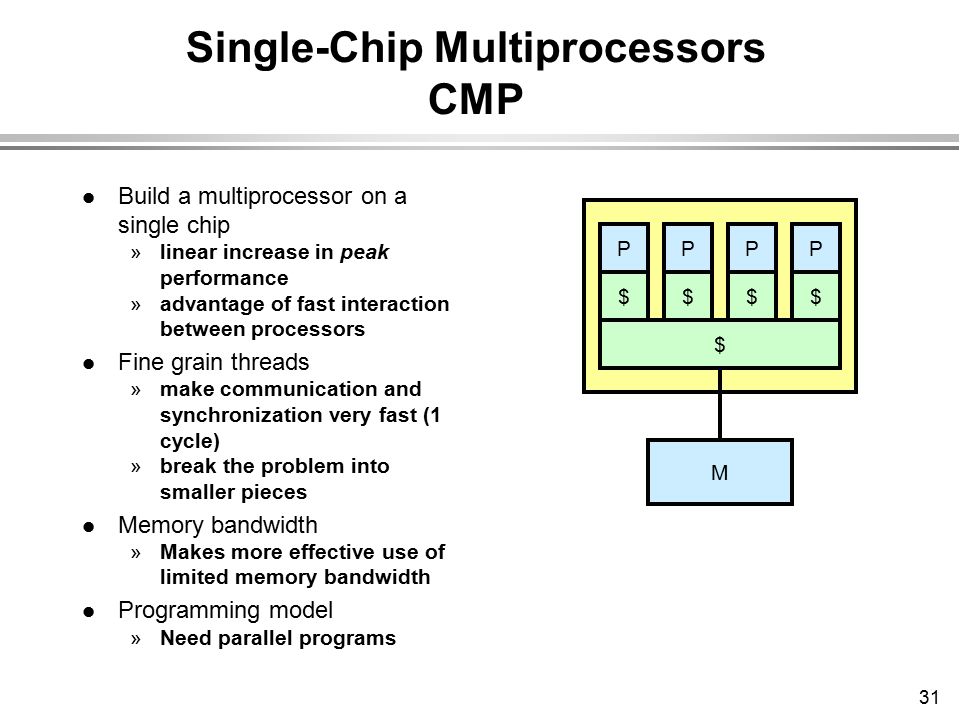

![PDF] Chip Multiprocessor: Challenges and Opportunities | Semantic Scholar PDF] Chip Multiprocessor: Challenges and Opportunities | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/1ab28dbbdc3bdebe1654cd0b3e30d9b4b67e0a74/7-Figure4-1.png)